法政大学国際文化学部

情報システム概論

担当 重定 如彦

2009年10月13日

第4回 ハードウェア(その2)

1. 主記憶装置の仕組み

コンピュータのプログラムやデータは普段はハードディスクなどの二次記憶装置に保存されていますが、二次記憶装置はデータの読み書きが遅いので、実際のプログラムの動作時には一旦プログラムやデータをデータの読み書きを高速に行える主記憶装置に読み込んでからプログラムを実行します。主記憶装置にはメモリセルと呼ばれる電気がたまっていれば1、たまっていなければ0という1ビットのデータを表現する装置が並んでいます。データを1ビット単位で扱うのは効率が悪いので、メモリの中ではメモリセルを8つ(ものによっては16個)ひとまとめにして扱い、それぞれにデータのいわゆる住所であるアドレス(番地)が数字(一般に16進数で表現します)で割り当てられています。例えばメモリのサイズが65536バイトの場合(0000)16〜(FFFF)16のアドレスが割り当てられます(16進数のFFFF=10進数の65535)。

ポイント

·

メモリに格納されたデータにはそれぞれアドレスが割り当てられる。

·

一つのアドレスに1バイト(ものによっては2バイト)のデータが格納される。

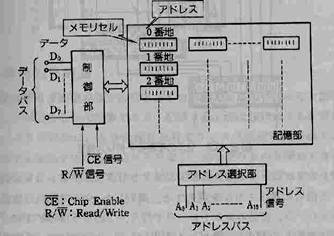

メモリは、下図のようにデータをメモリセルによって実際に記憶する「記憶部」、メモリの中のどのデータの読み書きを行うかを指定するための「アドレス選択部」、メモリのデータを読み書きする「制御部」から成っています。

アドレス選択部は読み書きを行いたいメモリのアドレスをA0〜A15までの16個、すなわち16ビット=2バイトのアドレス信号で指定します。制御部はR/W信号によって、「メモリからデータを読み込む」か「メモリにデータを書き込むか」を決めることができ、読み込まれたデータまたは、メモリに書き込むデータは、データバスと呼ばれるD0〜D8までの8個、すなわち8ビット=1バイトの信号で表します。

例えばメモリの(1234)16番地に格納されているデータを読み出すには、アドレス選択部に(1234)16を2進数になおした時のそれぞれの桁をアドレス信号として送ります。(1234)16は2進数になおすと(0001001000110100)2なので、アドレス選択部に送られるアドレス信号(1:電気が流れている、0:流れていない)は下の図のようになります。

|

A0 |

A1 |

A2 |

A3 |

A4 |

A5 |

A6 |

A7 |

A8 |

A9 |

A10 |

A11 |

A12 |

A13 |

A14 |

A15 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

制御部ではR/W信号に、データを読み込むということを表す信号を送ります。例えば0が書込み、1が読み込みを表す場合R/W信号に1を送ります。CE信号は、制御部のスイッチのようなもので、CE信号に信号を流している間だけ制御部が動作するので、読み込みや書き込み時には1を送ります。上記のアドレス信号、R/W信号、CE信号を送った結果、メモリの(1234)16番地の内容が読み込まれ、その内容がデータ信号としてデータバスに流れます。例えばメモリの(1234)16番地に56=(01010110)2というデータが格納されていた場合、データバスの8つの信号線には、以下の信号が送られます。

|

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

|

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

メモリにデータを書き込む場合は、データバスに書き込みたいデータ、アドレス選択部に書き込むメモリのアドレス、R/W信号に書込みの信号(上記の例の場合0)を送ると、指定したアドレスに指定したデータを書き込むことが出来ます。

2. 主記憶装置(メモリ)の内容

メモリには、中央処理装置(以下CPUと記述します)に指令を与えるための「プログラム」と、プログラムで使われる「データ」の2種類のものが格納されます。例えば、「メモリの4000番地から4128番地に格納されている数字の合計を計算せよ」という指令の手順を示したものが「プログラム」であり、「メモリの4000番地から4128番地に格納されている数字」が「データ」です。

プログラムは、機械語と呼ばれる言語で記述されます。機械語にはCPUに処理(=計算)を実行させるための様々な命令が用意されており、それぞれの命令は数バイトの数字で符号化されています。例えば、(00)16という数字が足し算を行うための命令、

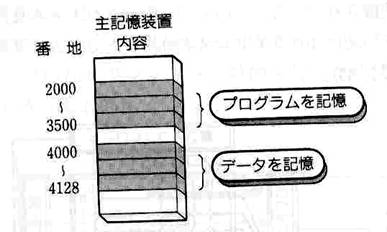

(01)16が引き算を行う為の命令のように、一つの数字がCPUに何らかの処理をおこなわせるための命令の意味を持っているのです。プログラムは、これらの機械語の数字の羅列で表現され、メモリの中に格納されます。プログラムは、プログラムが格納されたメモリのアドレスをCPUに渡す(知らせる)ことで実行されます。その際にCPUは指示されたアドレスに記述されている機械語の命令を順番に実行します。下の図は、プログラムがメモリの「2000番地から3500番地」、プログラムが扱うデータがメモリの「4000番地から4128番地」に格納されている状態を表しています。

メモリの中ではプログラムとデータはいずれも数字の羅列で表現されているため、見た目にはメモリの中身がプログラムであるかデータであるかの区別はできません。従って、データの部分をプログラムとして実行しようとすると正しく動かない点に注意が必要です。一見これは不便なことのように思えますが、プログラムとデータを混在させるということは非常に重要なアイディアです。メモリの中にプログラムとデータを混在させることができるコンピュータのことをプログラム内蔵式、別名「フォンノイマン型」コンピュータと呼び、現在のほとんどのコンピュータがこの方式で作られています。

プログラム内蔵型のコンピュータの利点は、メモリの中にプログラムを読み込むことができるため、同じ機械でいろんな作業を行うことができるという点にあります。プログラム内蔵式でない計算機の例としては、電卓がありますが電卓は四則演算などの限られた動作しか行えず、例えばワープロなどの他の用途には使うことはできません。一方コンピュータはプログラム(ソフト)をメモリに読み込んで実行することで例えばワープロとして使ったり、インターネットを見たり、メールを書いたりといろんなことに使うことができます。このように、コンピュータが一つのことだけでなく、いろんな用途につかうことができるのは、プログラム内蔵式の発明のおかげです。

3. 中央処理装置(CPU)の仕組み

CPUの仕事を一言で表すと、「メモリに格納されている機械語で書かれたプログラムを読み込み、その内容に従って計算を行う」となります。これを行う為に、CPUは以下の装置で構成されています。

·

演算装置(算術演算回路)

機械語の命令に従って数値の演算を行う為の計算回路で、固定小数点演算装置、浮動小数点演算装置、10進数演算装置、論理演算装置などがあります。最初の3つの装置は、それぞれの形式で表現された数値の四則演算などを行う装置です。論理演算装置は、後述する論理演算や、数値の大小の比較などを行う装置です。

·

レジスタ

レジスタは、演算装置などで使うデータを一時的に記憶させるための装置で、専用の目的をもったものと、汎用的につかうことができるものがあります。代表的なレジスタには以下のものがあります。

Ø

プログラムカウンタ

CPUはメモリに格納されているプログラムを一つ一つ順番に実行します。プログラムカウンタは、CPUが現在メモリの中のプログラムのどの部分を実行しているかを指すためのレジスタです。プログラムカウンタは機械語の命令をCPUが実行するたびに加算され、次に実行する機械語命令のアドレスを指すようになります。

Ø

メモリアドレスレジスタ

メモリのデータの読み書きを行う場合に、メモリのどの番地に対して処理を行うかを格納する為のレジスタで、メモリのアドレス選択部に送られます。

Ø

メモリデータレジスタ

メモリに対して読み書きしたデータを格納する為のレジスタです。このレジスタの内容はメモリの制御部につながっています。

Ø

命令レジスタ

メモリから読み込んだ機械語の命令を一時的に蓄えるためのレジスタです。

Ø

アキュムレータ

演算回路の演算に使うデータを一時的に蓄えるためのレジスタです。

Ø

フラグレジスタ

演算結果の数値の符合や、数字の大小関係を表すためのレジスタです。

Ø

汎用レジスタ

特定の目的に使われるのではなく、汎用的な目的で一時的にデータを蓄えるためのレジスタです。通常、汎用レジスタは複数個存在します。

·

バス

CPUの中でデータが流れる線の事をバスと呼び、以下の2種類があります。バスの太さ(バスに流すことができるデータのビット数)が太ければ太いほど一度に大きな桁数の計算を行えるのでコンピュータの性能が向上します。コンピュータの性能の指標のひとつに16ビットパソコン、32ビットパソコンといったように○○ビットパソコンと呼ぶ方法がありますが、この○○ビットは、バスの太さのことを表しています。

Ø

データバス

計算などに使用するデータが流れるバスでメモリの制御部に繋がっています。

Ø

アドレスバス

メモリのアドレスを指すデータが流れるバスでメモリのアドレス制御部に繋がっています

·

制御装置

CPUの各装置に対して制御命令を出す装置であり、以下の装置で構成されます。

Ø

命令制御部

命令レジスタに蓄えられた、次に実行する機械語の命令の種類をデコーダと呼ばれる装置を使って解読し、演算装置に適切な演算をおこなわせるための信号を送るための装置です。

Ø

記憶制御部

命令の実行に必要なデータをメモリからレジスタに読み込んだり、演算回路が行った演算結果をメモリに書き込むなど、メモリやレジスタに対するデータの読み書きの制御を司る装置です。記憶制御部はアドレスバスと呼ばれる信号線を使ってアドレス信号をメモリのアドレス選択部に送ります。また、メモリやレジスタで読み書きされるデータは、データバスと呼ばれる信号線を使って送られます

Ø

シーケンス制御部

機械語では、例えばある値が1より大きければメモリの2000番地に記述されている命令を実行、そうでなければメモリの3000番地に記述されている命令を実行するといった、条件によって命令の実行順序を制御する命令が用意されています。シーケンス制御部はこの命令の実行順序を制御するための制御装置です。シーケンス制御については次回以降の授業で解説します。

4. CPU制御の流れの例

それでは、具体的に例をあげて、CPUがどのように計算を行うかを見てみましょう。この例では、メモリの(2000)16番地から以下のようなプログラムが機械語で格納されておりそれを実行した場合CPUの中でどのような動作が行われるかを詳しく述べます。

1.

(2000)16:メモリの(4000)16番地の内容を汎用レジスタ1に読み込む。

2.

(2001)16:メモリの(4001)16番地の内容を汎用レジスタ2に読み込む。

3.

(2002)16:汎用レジスタ1と汎用レジスタ2の中身を加算し、結果を汎用レジ

スタ3に格納する。

4.

(2003)16:汎用レジスタ3の内容をメモリの(4002)16番地に書き込む。

上記のプログラムを実行すると、メモリの(4000)16番地の内容とメモリの(4001)16番地の内容が加算され、メモリの(4002)16番地に書き込まれます。

前準備として、あらかじめメモリの(4000)16番地に数字の1、(4001)16番地には数字の2、プログラムカウンタにはこれから実行するプログラムが格納されているメモリの先頭の番地である(2000)16を格納されているものとします。従ってプログラムの実行前では、それぞれのレジスタやメモリの内容は以下のようになっています。

なお、PCはプログラムカウンタ、GR1〜GR3は汎用レジスタ1〜汎用レジスタ3を表し、?は値が設定されていないため内容が不明であることを表します。また、表の中の数値はすべて16進数です。

|

レジスタ |

|

メモリ |

|||||

|

PC |

GR1 |

GR2 |

GR3 |

|

4000 |

4001 |

4002 |

|

2000 |

? |

? |

? |

|

1 |

2 |

? |

1.

PCの指すメモリの内容を読み込み、命令レジスタに格納する。具体的にはまずPCの内容をアドレスバスを経由してアドレス選択部に送り、これから実行する機械語の命令が格納されたメモリのアドレスの番地を指定します。そして、同時にメモリの制御部のR/W信号に読み込み信号を送ることで、メモリから(2000)16番地の内容が読み出だされ、その内容がデータバスを通って命令レジスタに格納されます。

2.

命令レジスタの内容をデコーダに送り、(2000)16番地の命令の内容を解読する。

3.

命令の内容は「メモリの(4000)16番地の内容を汎用レジスタ1に読み込む」なので、メモリの(4000)16番地の内容を読み込んでGR1に格納する。読み込む具体的な手順については1と同様です。

4.

命令の実行が終了したので、PCの内容を1加算する。この結果レジスタとメモリの内容は以下のように変化します(変更された部分は灰色でぬりつぶされています)。

|

レジスタ |

|

メモリ |

|||||

|

PC |

GR1 |

GR2 |

GR3 |

|

4000 |

4001 |

4002 |

|

2001 |

1 |

? |

? |

|

1 |

2 |

? |

5.

上記の1〜4の作業を再び行い、メモリの(2001)16番地に記述されていた、「メモリの(4001)16番地の内容を汎用レジスタ2に読み込む」を実行する。

|

レジスタ |

|

メモリ |

|||||

|

PC |

GR1 |

GR2 |

GR3 |

|

4000 |

4001 |

4002 |

|

2002 |

1 |

2 |

? |

|

1 |

2 |

? |

6.

次に、(2002)16番地の「汎用レジスタ1と汎用レジスタ2の中身を加算し、結果を汎用レジスタ3に格納する」を実行する。この時、GR1とGR2の内容がデータバスを通り算術演算回路に渡される。演算回路は合計の演算を行い、その出力結果をGR3に格納する。

|

レジスタ |

|

メモリ |

|||||

|

PC |

GR1 |

GR2 |

GR3 |

|

4000 |

4001 |

4002 |

|

2003 |

1 |

2 |

3 |

|

1 |

2 |

? |

7.

最後に(2003)16番地の「汎用レジスタ3の内容を(4002)16番地に書き込む」が実行され、(4002)16番地に1+2の演算結果である3が格納される。

|

レジスタ |

|

メモリ |

|||||

|

PC |

GR1 |

GR2 |

GR3 |

|

4000 |

4001 |

4002 |

|

2004 |

1 |

2 |

3 |

|

1 |

2 |

3 |

上記の例は非常に小さなプログラムの実行例でしたが、大きなプログラムでもこの手順は変わらず、こうしたことの繰り返しでCPUはプログラムを実行します。

5. 演算回路の仕組み

CPUの具体的な制御の流れは大体上記のとおりですが、次に具体的な演算を行う演算回路がどうやって計算を行っているかについて説明します。

·

論理演算

演算回路の説明をおこなう前に、演算回路で使われる論理演算について説明します。論理演算は1つまたは、2つの1ビットの数字の演算で、AND、OR、NOTの3種類の演算があります。ANDは2つの1ビットの数字が共に1であった場合のみ1を計算結果として返すという演算で、日本語でいえば、「かつ」に相当します。2つの1ビットの数字の組み合わせは4通りあるので、

0 AND 0 = 0

0 AND 1 = 0

1 AND 0 = 0

1 AND 1 = 1

となります。これを表にまとめると以下のようになります。

|

AND演算 |

0 |

1 |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

ORは2つの1ビットの数字のどちらか片方が1の場合1を返すという演算です。日本語でいうと「又は」になり、表になおすと以下のようになります。

|

OR演算 |

0 |

1 |

|

0 |

0 |

1 |

|

1 |

1 |

1 |

NOTはANDとORとは異なり一つの1ビットの数字を反転、すなわち1を0に、0を1にする演算です。

NOT 0 = 1

NOT 1 = 0

ここまでは、1ビットの数字の論理演算を説明しましたが、複数ビットの数字の論理演算も可能です。複数ビットの場合、それぞれの桁ごとに演算をおこないます。2進数以外の数の論理演算をおこなう場合は、一旦2進数になおしてから計算する必要がある点に注意して下さい。なお、ANDやORの演算で片方の数字の桁の数が少ない場合は足りない部分に0をおぎなって計算します。また、NOTの場合は何桁で計算するかをあらかじめ決めておく必要があります。

例1: (10011)2 AND (1110)2 を演算する場合、以下のように縦に数字を並べ、それぞれの桁をAND演算すればよい。

(10011)2

AND (01110)2

答えは (00010)2

例2: 10進数の9を8桁の2進数でNOT演算するには、まず9を一旦8桁の2進数になおしてから演算します。9を8桁の2進数に直すと(00001001)2 になり、この各ビットの数字を反転すれば良いので答えは (11110110)2 です。

·

課題1

授業の最初で説明したメモリ装置の(9ABC)16番地に、(6E)16というデータを書き込むためには、アドレスバスにどのようなアドレス信号(A0〜A15)を、データバスにどのようなデータ信号(D0〜D7)、R/WおよびCE信号にどのような信号を送ればよいか記述せよ。なお、信号は0=電流が流れていない状態、1=電流が流れている状態として記述すること。

·

課題2

以下の論理演算を行い、答えを2進数で示せ。

Ø

(11011)2 OR (1101)2

Ø

NOT 109 (ただし、109は10進数。答えは2進数8桁で)

Ø

(6C)16 AND (D9)16

·

論理回路

上記のAND、OR、NOTは、電気回路になおすことが出来ます。例えばAND回路はリレーを使って以下のように作成することが出来ます。

上記の回路では電球にランプを点灯させるには、内側の2つのスイッチを両方ともONにする必要がありますが、これはまさに、両方とも1(スイッチがON)の場合だけ1(電球が点灯する)を返すというAND回路を表します。同様の方法で、OR回路やNOT回路を作ることができます。

なお、実際の論理回路はリレーではなく、高速な電子回路を使って作られていますが、原理はリレー回路と同じです。

6. 課題

このプリントの課題1と2を行い課題のメールとして提出して下さい。

締め切りは来週の授業までです。

課題のメールは masaki.yamashita.67@gs-art.hosei.ac.jp までお願いします。

質問のメールなどは、sigesada@.hosei.ac.jpまでお願いします。

授業の資料の最新版はhttp://www.edu.i.hosei.ac.jp/~sigesada/にあります。